Lattice GAL16V8D-15LPNI: Architecture, Features, and Application Design Considerations

The Lattice GAL16V8D-15LPNI stands as a classic and highly influential device in the history of programmable logic. As a member of the Generic Array Logic (GAL) family, it provided a revolutionary, erasable alternative to one-time programmable PALs, significantly accelerating prototyping and development cycles. This article delves into its internal architecture, key features, and critical design considerations for modern applications.

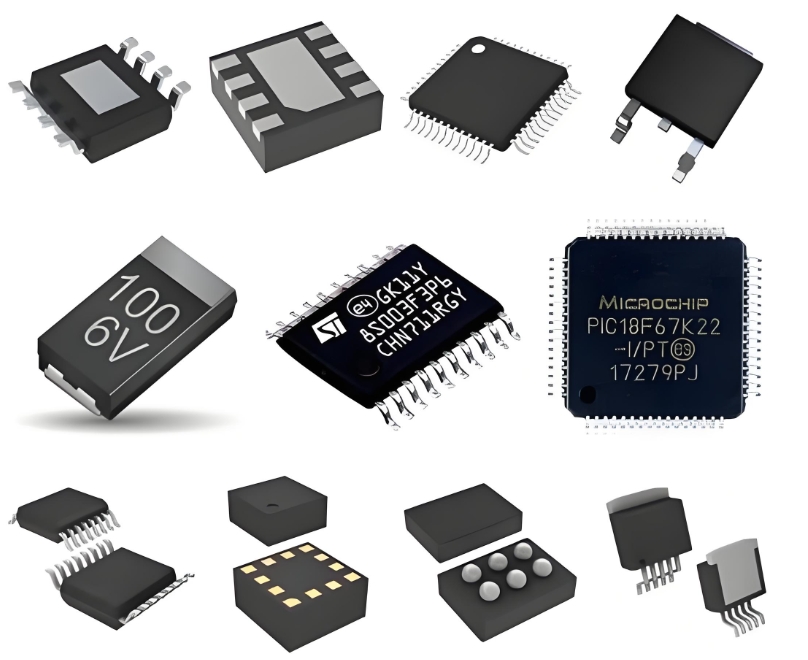

Architecture: A Look Inside

The GAL16V8D's architecture is a masterpiece of structured programmability. Its name reveals its core configuration: a maximum of 16 inputs and 8 outputs. The outputs are configured through a highly versatile output logic macrocell (OLMC), which is the heart of its flexibility.

The internal structure consists of:

Programmable AND Array: This is a fixed matrix that forms the product terms (AND operations) for the device's logic functions. The user programs the connections within this array to define the desired logic.

Fixed OR Array: Unlike earlier PLDs, the GAL family uses a distributed OR array. Each OLMC sums a specific set of product terms from the AND array.

Output Logic Macrocell (OLMC): This is the key to the device's reconfigurability. Each of the eight outputs can be individually configured as a combinatorial output, a registered (clocked) output, or an input. This is controlled by programming specific architecture bits, allowing a single device to replace numerous fixed-function logic ICs.

Key Features and Specifications

The "D" in its part number signifies a commercial temperature range device, while the "-15" denotes a maximum pin-to-pin propagation delay of 15 ns, making it suitable for moderately high-speed logic. The "LPNI" indicates the low-power, plastic dual-in-line (PDIP) package.

Primary features include:

High Performance: 15 ns maximum propagation delay.

Low Power Consumption: Utilizing a CMOS process, it draws significantly less current than bipolar PAL equivalents.

Electrically Erasable (EE) CMOS Technology: The device can be reprogrammed, typically over 100 times, allowing for design iterations and corrections.

Eight Versatile OLMCs: Enables complex state machine and registered logic design.

100% Testability: The internal logic provides complete functionality and AC test access.

Application Design Considerations

While a legacy device, the GAL16V8D-15LPNI remains relevant for specific use cases. Key considerations for its implementation include:

1. Logic Density: Its capacity is limited to roughly 20 to 25 logic gates per macrocell. It is ideal for "glue logic" – address decoding, state machine control, bus interfacing, and I/O expansion. Complex algorithms or large data paths are beyond its scope.

2. Power-On Reset and State: The registered outputs have a defined power-on state, which is crucial for designing predictable system initialization sequences.

3. Clock and Timing Constraints: Designers must carefully consider the 15 ns timing limitation, especially when interfacing with modern microprocessors or other high-speed components. Setup, hold, and clock-to-output times must be rigorously verified.

4. Modern Development Tools: Support in contemporary EDA tools can be limited. Design often relies on older software or hardware description languages (HDLs) like VHDL or Verilog, followed by careful fitting to ensure the design does not exceed the available product terms.

5. Obsolescence and Replacement: For new designs, it is often more practical to use modern CPLDs or FPGAs that offer greater density, speed, and lower cost. The GAL16V8 is primarily used for maintaining or repairing existing legacy systems.

The Lattice GAL16V8D-15LPNI was a cornerstone of digital design, bridging the gap between simple fixed logic and complex programmable devices. Its innovative OLMC architecture and EECMOS technology provided unprecedented design flexibility and reusability for its time. For engineers today, understanding its structure is key to maintaining legacy systems, while its design constraints offer a fundamental lesson in efficient logic synthesis within limited resources.

Keywords:

Programmable Logic Device (PLD)

Generic Array Logic (GAL)

Output Logic Macrocell (OLMC)

Logic Synthesis

Glue Logic